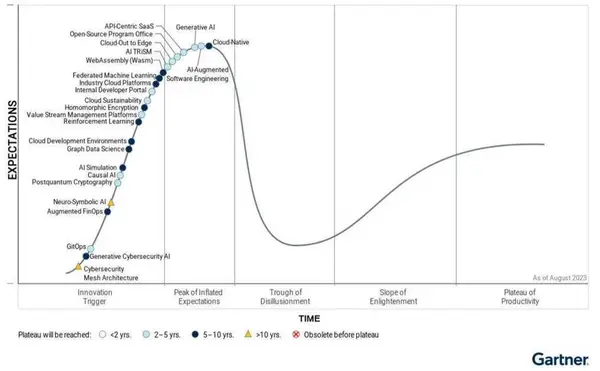

在全球数字化和智能化浪潮的推动下,人工智能(AI)技术正以前所未有的速度发展。根据市场研究机构Gartner 的数据,AI芯片市场在过去几年中呈现出爆发式增长的态势。根据预测,2024 年全球AI半导体市场规模将增长 25.6%,达到 671 亿美元,并预计在未来几年将继续保持高速增长。到2027年,市场规模预计将达到 1194 亿美元,年均增长率超过30%。

趋势▹AI芯片的增长需求

AI芯片的快速增长得益于AI技术在各个行业的广泛应用,如自动驾驶、智能制造、医疗健康等。AI算法和计算能力的不断提升,使得对高性能AI芯片的需求急剧增加,数据量的爆炸式增长,进一步推动了对更高效数据处理和分析的需求。

生成式AI(Generative AI)作为AI技术的重要分支,其在图像、文本、音频等多模态数据的生成和处理方面展现出了强大的能力。生成式AI的应用范围广泛,从内容创作、虚拟现实、游戏开发到医疗图像生成等,各个领域都对AI芯片提出了更高的需求。生成式AI对芯片的拉动主要体现在以下几个方面:

·算力需求增加:生成式AI模型,如GPT-4、DALL-E等,通常需要庞大的计算资源进行训练和推理。这对AI芯片的算力和效率提出了极高要求,推动了高性能芯片的研发和生产。

·能效比优化:生成式AI应用中,大规模模型的训练和推理过程消耗大量能源。如何在提升算力的同时降低能耗,成为芯片设计和制造的关键挑战。

·存储和带宽需求:生成式AI处理的数据量巨大,对存储和带宽的要求也随之提升。这需要AI芯片在存储架构和数据传输方面具备更高的性能。

制造▹AI芯片封装工艺

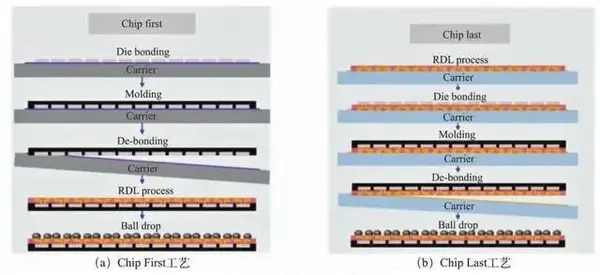

AI芯片的制程既复杂又严谨,算力和功耗是其性能的两个关键指标,在后摩尔时代,提升算力和降低功耗越来越依赖于重布线层(RDL)、硅通孔(TSV)、硅中介层和微凸点等先进封装技术。目前,主要的先进封装技术有扇出型(FO)封装、2.5D/3D封装和Chiplet技术等。

◎ FO封装技术

FO封装通过RDL和焊锡球将芯片焊盘从芯片边缘"扇出"连接到PCB上,从而增加可用布线区域,充分利用芯片面积,降低成本。它的优势在于无需封装载板,直接焊接到PCB上,缩短信号传输距离,提高电学性能。FO封装技术已广泛应用于人工智能、5G通信、毫米波雷达等领域。

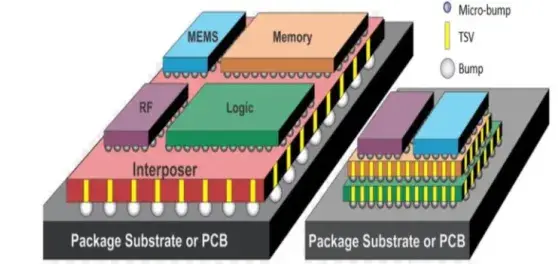

◎ 2.5D/3D封装技术

3D集成技术通过TSV实现不同芯片层之间的电学互连,包括3D IC封装、3D IC集成和3D Si集成。3D-IC封装可以容纳多个异构裸片,各功能模块可采用不同的制程节点,降低成本,加快产品上市速度。3D-IC技术支持更小尺寸,节省空间,适用于小型移动设备。该技术在CPU、GPU、智能手机、高性能计算等领域有广泛应用,是延续摩尔定律的有效路径之一。

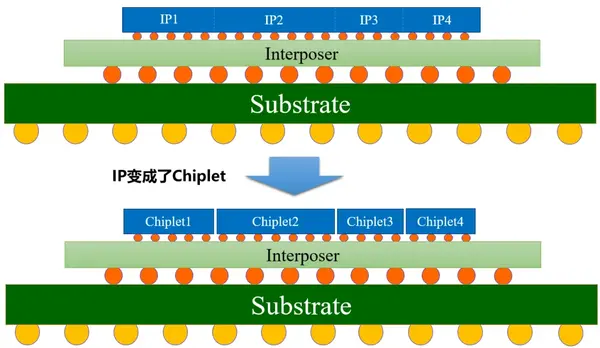

◎ Chiplet技术

Chiplet是一种设计概念,将复杂的SoC芯片分散成多颗具有特定功能的芯粒,再通过封装技术整合成多功能的异构SiP。与传统单芯片方案相比,Chiplet方案具有更高的设计良率和更低的成本。研究表明,当芯片面积较大时,Chiplet方案的良率显著高于单芯片方案。Chiplet技术还允许不同工艺下的芯片封装连接,提高封装灵活性,提升先进工艺的利用效率,降低成本。

赋能▹高精度贴装解决方案助力量产

与此同时,复杂的运行环境对AI芯片的稳定性和可靠性也有严格要求。高精度固晶机设备发挥着至关重要的作用,其中,精度、速度、稳定性是最核心的指标。博众半导体的产品及贴装解决方案可以为制造商提供高精度的固晶和共晶贴片工艺,助力制造商生产高性能的AI芯片。

博众半导体高精度固晶贴片机精度可达0.5-3μm,兼备多头贴装能力,可以同时处理多种芯片贴片,提高生产效率,满足大规模量产的需求。值得一提的是,AI芯片贴片的共晶工艺需要在高温下进行,星威系列共晶机具备良好的温控能力,升温仅需3.2s,冷却仅需6.5s,能够在整个工艺过程中保持稳定的温度环境,确保焊料的均匀熔化和芯片的可靠贴装。且整机采用模块化设计,具备高度的灵活性,能够适应不同尺寸和类型的芯片,满足多样化的生产需求。

在未来,我们可以预见,随着高精度共晶机技术的进一步发展和创新,AI芯片的制造将变得更加精密和高效。这不仅将促进各行各业的智能化转型,也将为我们的生活带来更多便利和可能性。